Product Summary

The MT46V16M16P-75:F is a double data rate SDRAM. The device is a high-speed CMOS, dynamic random-access memory that operates at a frequency of 167 MHz (CK=6ns) with a peak data transfer rate of 333Mb/s/p. The MT46V16M16P-75:F continues to use the JEDEC standard SSTL_2 interface and the 2n-prefetch architecture.

Parametrics

MT46V16M16P-75:F specifications: (1)Delta Input/Output Capacitance: DQs, DQS, DM (for x4 or x8 devices)DCIO: max=0.50pF; (2)Delta Input Capacitance: Command and Address DCI1: max=0.50pF; (3)Delta Input Capacitance: CK, CK# DCI2: max=0.25pF; (4)Input/Output Capacitance: DQs, DQS, DM (LDQS, LDM, UDM)CIO: min=3.50pF, max=4.00pF; (5)Input Capacitance: Command and Address CI1: min=1.50pF, max=2.50pF; (6)Input Capacitance: CK, CK# CI2: min=1.50pF, max=2.50pF; (7)Input Capacitance: CKE CI3: min=1.50pF, max=2.50pF.

Features

MT46V16M16P-75:F features: (1)Internal, pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle; (2)Differential clock inputs (CK and CK#); (3)Commands entered on each positive CK edge; (4)DQS edge-aligned with data for READs; center-aligned with data for WRITEs; (5)DLL to align DQ and DQS transitions with CK; (6)Four internal banks for concurrent operation; (7)Data mask (DM) for masking write data (×16 has two - one per byte); (8)Programmable burst lengths: 2, 4, or 8; (9)Concurrent Auto Precharge option supported; (10)Auto Refresh and Self Refresh Modes; (11)FBGA package available; (12)2.5V I/O (SSTL_2 compatible).

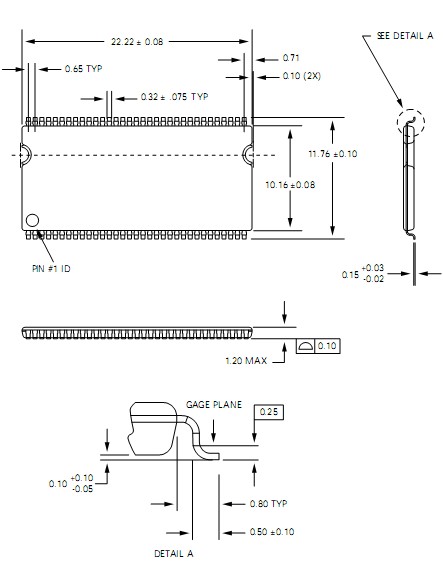

Diagrams

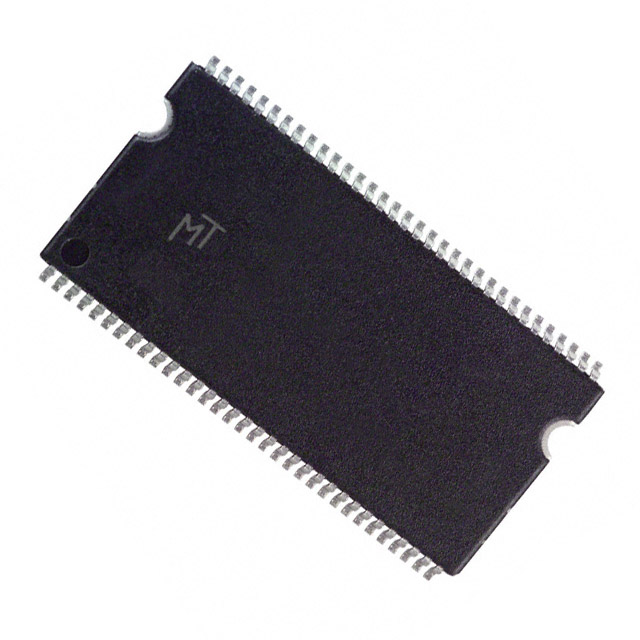

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

MT46V16M16P-75:F |

|

IC DDR SDRAM 256MBIT 66TSOP |

Data Sheet |

Negotiable |

|

||||

|

MT46V16M16P-75:F TR |

|

IC DDR SDRAM 256MBIT 66TSOP |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))